EMCにおける実装設計

2025.08.20

これまで50社以上の電子機器の設計開発におけるEMC問題の解決をご支援してきた図研テックの視点で「パワーエレクトロニクスにおけるEMC実装設計」を連載テーマに、プリント基板(PCB)を中心に実装技術の要素を交えてEMC対策について解説します。

連載記事一覧

<EMC設計関連>

<熱設計関連>

この記事の目次

本記事の執筆者:図研テック株式会社 技術監督 古瀬 利之(プロフィール)

図研テックでは、「設計者によってEMC対策に対する考え方が異なるため、設計品質が安定しない」「開発テーマによって、EMC対策の効果の有無が変わるため、何から手を付ければ良いかわからない」「EMCに関する設計手順や基準が無いため、新規製品開発でEMC問題が起こりがち」といったお客様に、EMC対策の技術的な支援と、EMC設計プロセスの構築・標準化を中心とした業務改革の支援を行っています。→「設計・解析コンサルティング」サービス紹介ページ

はじめに

前回は、パワーエレクトロニクス(=パワエレ)の市場動向やEMCに関する問題点について記事にまとめました。

今回はEMCにおける実装設計と題して、電気/電子機器全般の実装設計とEMCの関係について解説します。

実装設計とは?

実装という用語は、読者によって解釈や捉え方が異なる場合があるかもしれません。

実装は電気設計(ハードウェア設計)だけではなく、ソフトウェア開発でも使われるため、さらにこの用語をわかり難くしています。

本題に移る前に「実装設計とは何か?」、日本国内の実装技術に関する中核組織である一般社団法人エレクトロニクス実装学会(JIEP)の「回路・実装設計技術委員会」のWebページから、同委員会の活動目的の説明箇所を引用します。

「チップ」「パッケージ」「ボード」等の個々のレベルの「デザイン」「CAD」「CAE」のエレクトロニック・デザイン・オートメーション(EDA)技術、及び構造/熱/電気等を連成したマルチフィジックス・シミュレーションの技術を主対象とした動向調査、課題抽出を行う。

出典:一般社団法人エレクトロニクス実装学会

https://www.jiep.or.jp/tech-committees/circuit.html

少し難しい表現ですが、実装設計とは、電気・電子回路といった論理的で実体のない構成を、プリント基板(PCB)を中心とした物理的かつ具体的な形に落とし込む作業を指す用語、と要約できます。

本記事ではそれに加えて、電気・電子回路を構成する物理的な形状の設計全般を実装設計と捉えて、実装設計とEMCの関係性について解説します。

本記事における「実装設計」の定義

- 電気・電子回路を接続させるための具体物(PCB、ケーブル等)の設計

- それらを物理的に支えて構成する具体物(筐体、機構部品等)の設計

- EMCだけでなく、熱、信頼性、製造性、コスト等の観点で最適解となるような設計

EMCとパッケージ形状

同じ性能の半導体、受動部品でも部品の物理形状、いわゆるパッケージ形状によりEMC性能が変わります。IC等の半導体用のパッケージは、ダイ(半導体チップ)を銅や銀のワイヤを使用してリードに接続するため、これらの形状・材質がEMC性能に影響を及ぼします。

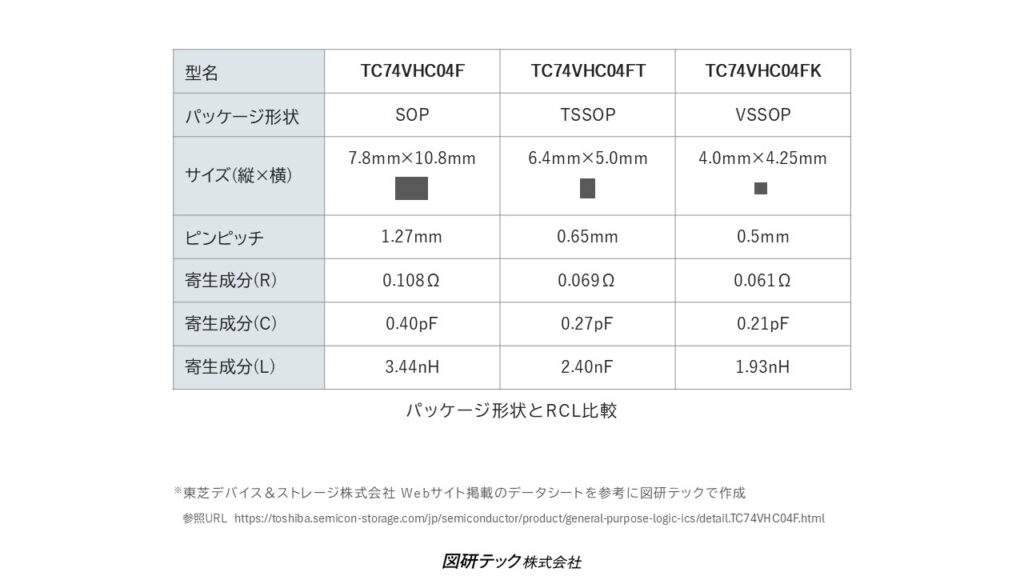

具体例として、東芝デバイス&ストレージ株式会社のWebサイトで公開されている東芝製74VHCシリーズICのデータシートのIBISモデルを参考に、パッケージ形状とRCLの寄生成分の相関を見てみます。

このように、狭ピッチの小型パッケージになるほど、リードの物理形状が小さくなり、それに伴い寄生成分も小さくなります。

また、受動部品(抵抗、コンデンサ、コイル)も同様にチップ形状、特に電極形状が寄生成分に影響します。

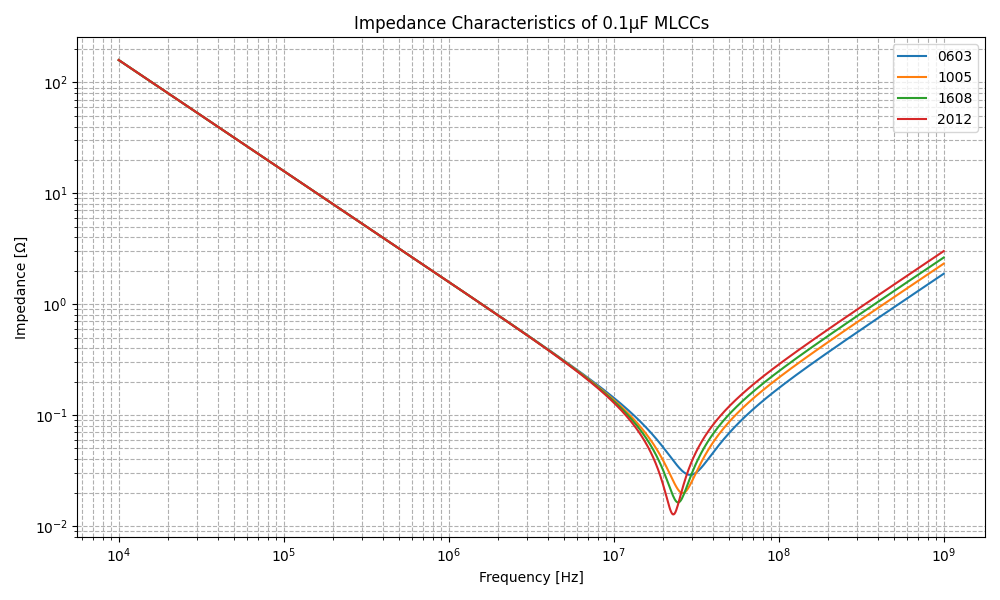

下図は、一般的な0.1μFのMLCCにおけるチップサイズとインピーダンス特性のグラフです。

自己共振周波数までのインピーダンスは容量成分が支配的ですが、自己共振周波数以降はチップ形状に含まれる寄生インダクタンス(ESL)が支配的であるため、ほぼチップサイズに依存した特性であることがわかります。

一般的な電気・電子機器の設計で半導体パッケージやチップ形状そのものの設計を行うケースは非常に稀ですが、適切な部品の選定は設計の範疇であるため、EMC性能を考慮して適切な形状の部品を選定することは、電気・電子回路の設計において非常に重要です。

また、EMCだけではなく、熱、信頼性、製造性なども考慮して、最適な部品を選定することが実装設計の本質と言えるのではないでしょうか。

EMCとPCB設計

EMC性能において、プリント基板(PCB)の実装設計の影響が非常に大きいことについては、読者の皆様も異論は無いと思います。

PCBの配線に信号や電源の電流が流れることで電磁波が生じますが、配線の引き回しやGNDシールドの有無などにより、発生する電磁波の大きさが変わります。

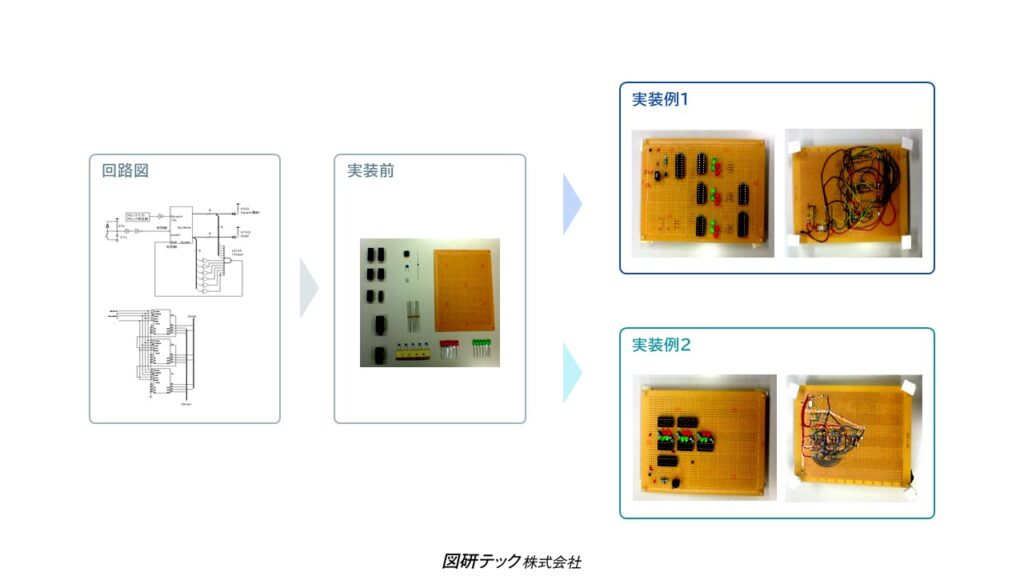

ここで、配線の引き回しの違いによるEMIノイズの変化について、弊社で実験した例をご紹介します。

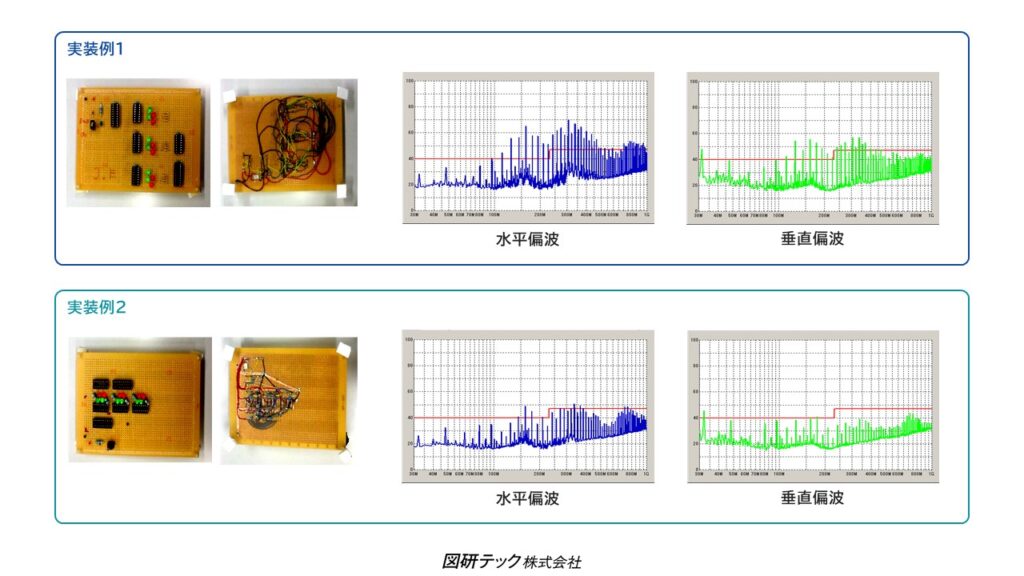

部品の配置間隔が広く、配線も少々煩雑な「実装例1」に比べて、部品配置と配線をコンパクトにまとめた「実装例2」の方が、EMIノイズも非常に少ない結果となりました。

その理由は、冗長な配線を行うことにより、配線から電磁波が生じてしまうためであると考えられます。また、ノイズ対策がほとんど施せないユニバーサルボードでの配線であることも影響して、「実装例1」では大きな電磁波ノイズが発生しています。

なぜ冗長な配線がノイズ発生の要因となるかについては、この連載の中で別の機会に解説します。ここでは適切な部品レイアウト・配線を行うことによって、電磁波ノイズの発生が大幅に削減できることを、まずはご理解ください。

余談ですが、私が駆け出しの設計者だった頃、「きれいに配線されたPCBはノイズに強い」と先輩に指導されました。この実験では、その格言の通りの結果となっています。

EMCとケーブル設計

PCBやユニット間を接続するケーブルについても、PCB内の配線と同様に信号や電源の電流が流れるため、EMC性能に影響を及ぼします。

また、EMCを考慮したPCBの多くは多層板を採用することで、GNDベタ層を設けてノイズの影響を小さくしていますが、ケーブルについては構造的な問題や配線も長くなりやすいことなどから、PCBよりノイズへの影響が大きいケースが多いです。

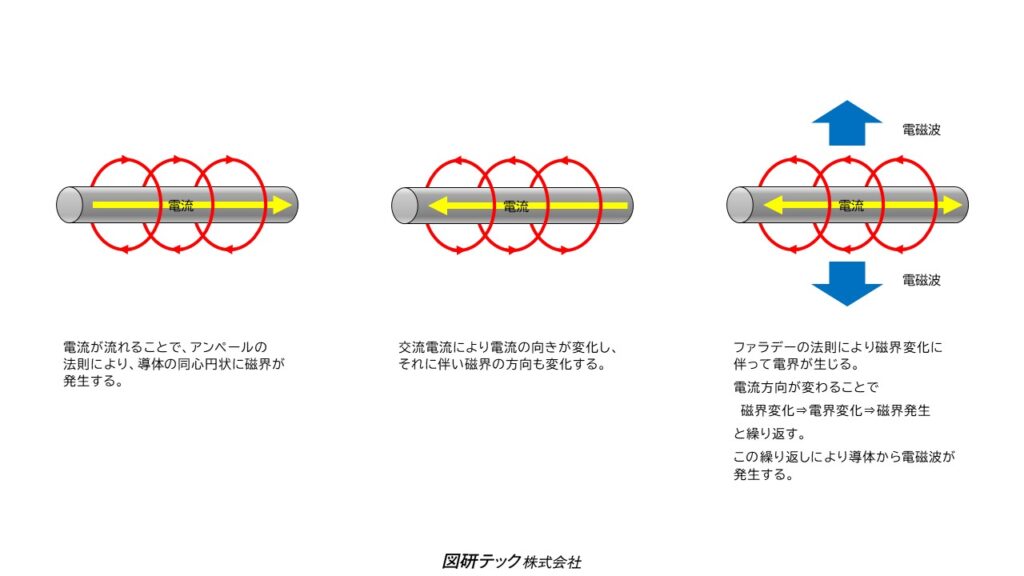

例えば、1本のワイヤに交流電流が流れると、アンペールの法則により磁界が発生します。さらに、電流の向きが変化することで磁界も時間的に変化し、それに伴ってファラデーの法則により電界が生じます。

こうした電場と磁場の変化が繰り返されることで、電磁波が発生します。

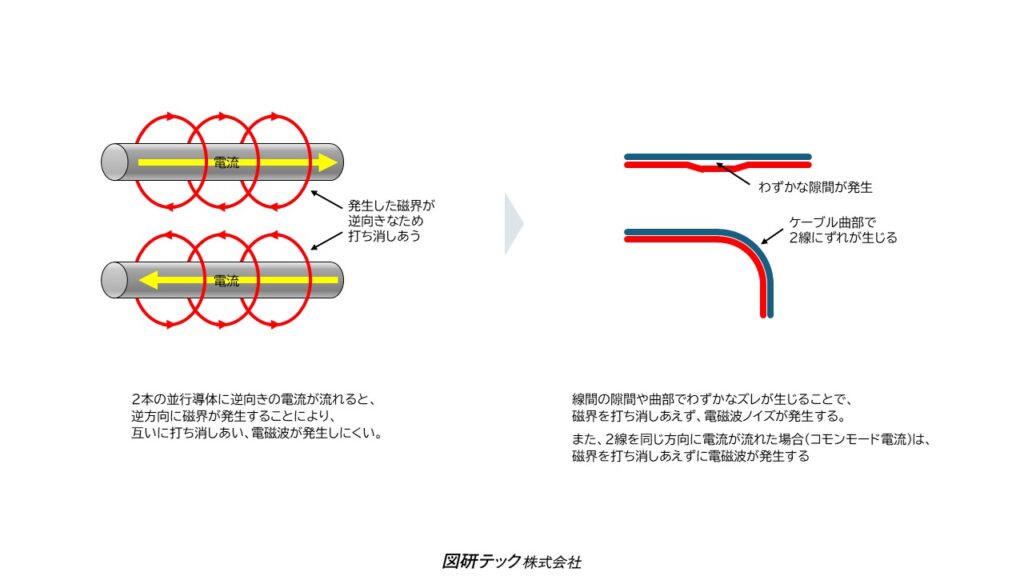

この発生した電磁波に対して、電源/GNDや差動信号のように2本のワイヤで伝達させる場合、2線が並行している状態であれば互い発生する磁界の向きが逆向きなため、打ち消しあうことで電磁波が出づらくなります。

ただし、湾曲部などの並行状態が完全でない箇所や微妙な距離の違いなどで完全に打ち消しあうことができず、多少なりとも電磁波ノイズが発生します。この場合、2線同士をツイストすることで、電磁波の発生をより抑えることが可能です。

(この原理についても、本連載の中で詳しく触れる予定です。)

上記のように電流が2線で逆方向に同じだけ流れる場合だけでなく、複数のワイヤを束ねただけの束線ケーブルについては、発生する磁界を打ち消しあうこともできず、大きな電磁波ノイズを発生することがあります。

その場合は、ケーブルそのものにシールドを施したり、シールドタイプのFFCに置き換えるなどの対策が必要です。

ただし、シールドの接地処理により、逆効果になるケースもあるため注意が必要です。

EMCと筐体設計

PCBやケーブルとは異なり、筐体に意図的に信号や電源の電流を流すことは通常ありません。

しかし、筐体を基準電位(GND)として扱う場合や、PCBやケーブルの固定という観点から見ると、筐体設計も実装設計の一部と考えることができます。

EMC的な観点から考えると、筐体内におけるグラウンディング(接地)も重要ですが、筐体をシールドの一部としたPCBやケーブルのノイズ対策も非常に重要です。

また、静電気試験においては、PCBやケーブルに静電気ノイズが侵入しないような筐体設計が必要です。

最後に

今回は、一旦、パワーエレクトロニクスの話題から離れて、「実装設計」について、読者の皆様とイメージを共有することを目的に、実装設計とEMCの関係にフォーカスした内容としました。

これを踏まえて次回の連載では、パワエレにおけるノイズ発生の仕組みや伝わり方について、原理・原則に基づいて解説する予定です。

図研テックではEMC設計・対策を支援する「EMC設計支援サービス」やEMC、パワエレに関するスキルアップを支援する「eZラーニング(イージーラーニング)」のサービスを提供をしています。ご興味のある方は以下のリンクから詳しいサービス紹介をご覧ください。>

連載記事一覧

<EMC設計関連>

<熱設計関連>

この記事の執筆者

図研テック株式会社 技術監督 古瀬 利之

iNARTE EMC Master Design Engineer (Certificate No.EMCD-00243-ME)

1999年株式会社図研プロセスデザイン研究所(現、図研テック株式会社)に入社。

EMC設計・対策、高速半導体用インターポーザ、携帯電話用PCBを中心に電気設計業務を担当。

2014年よりEMC設計支援サービスやEMC設計教育サービスを立ち上げ、2021年より現職。

-

- KEC関西電子工業振興センター

iNARTE EMC設計技術者資格試験問題作成部会委員(2016-2018) - KEC関西電子工業振興センター主催 設計者向けEMC技術講座

「EMC設計におけるフロントローディングとデザインレビュー」

講師(2016-2019) - 環境電磁工学研究会(EMCJ)主催

第14回 EMC基礎ワークショップ 講師(2018) - ポリテクセンター中部主催

ディジタル回路のEMC実践技術講座 講師(2021-) - 第31回エレクトロニクス実装学会春季講演大会

講演大会優秀賞受賞

受賞講演「部品内蔵基板設計におけるCAE活用と、テスト容易化設計技術の展望」

- KEC関西電子工業振興センター

提供サービスのご紹介

「EMC設計支援サービス」の詳しい説明は、こちらの資料をご覧ください。

EMC設計をはじめエンジニアの育成・スキルアップにご興味をお持ちの方は、

「eZラーニング(イージーラーニング)」のサービス紹介ページをご覧ください。

メールマガジン『ZUKEN TEC NEWS』では、

設計や解析技術、CAD運用に関する情報や、図研テックのエンジニアが登壇するセミナーのご案内などをお届けしています。