パワエレにおけるEMCノイズ(後編)

2026.01.14

これまで50社以上の電子機器の設計開発におけるEMC問題の解決をご支援してきた図研テックの視点で「パワーエレクトロニクスにおけるEMC実装設計」を連載テーマに、プリント基板(PCB)を中心に実装技術の要素を交えてEMC対策について解説します。

連載記事一覧

<EMC設計関連>

-

- パワーエレクトロニクスにおけるEMC問題

- EMCにおける実装設計

- パワエレにおけるEMCノイズ(前編)

- パワエレにおけるEMCノイズ(後編) <本記事>

- パワエレにおけるノイズの伝わり方

- DC-DCコンバータにおけるノイズと基板レイアウト

<熱設計関連>

図研テックでは、「設計者によってEMC対策に対する考え方が異なるため、設計品質が安定しない」「開発テーマによって、EMC対策の効果の有無が変わるため、何から手を付ければ良いかわからない」「EMCに関する設計手順や基準が無いため、新規製品開発でEMC問題が起こりがち」といったお客様に、EMC対策の技術的な支援と、EMC設計プロセスの構築・標準化を中心とした業務改革の支援を行っています。→「設計・解析コンサルティング」サービス紹介ページ

はじめに

前回は、「パワエレにおけるEMCノイズ(前編)」と題して、ノイズの分類とパワーエレクトロニクス(以降、パワエレ)におけるノーマルモードノイズについて解説しました。

後編の今回はパワエレにおけるコモンモードノイズについて解説します。

コモンモードノイズとは?

パワエレにおけるコモンモードノイズの解説に先だって、まずはコモンモードノイズそのものについて解説します。

専門書ではコモンモードノイズについて、以下のように教科書的な説明が記載されていることが多いと思います。

コモンモードノイズとは、複数の導体に対して同相で現れる電圧変動や、それに伴う電流によるノイズであり、主に配線と筐体間の浮遊容量などを介して伝搬します。

私もそうでしたが、このような説明では、なぜ同相にノイズが発生するのかイメージがつきづらく、コモンモードノイズの本質がなかなか理解できません。

コモンモードノイズの理解を難しくしている大きな要因は、以下の2つではないでしょうか?

- ノーマルモードと異なり、直感的理解がしにくい

- ノイズの経路が分かりにくい

そもそも、ノーマルモード/コモンモードという区別は、自然界に存在する現象でなく、あくまでも人間が回路解析やEMC対策を行いやすくするために便宜的に導入した概念です。

自然界(電磁界)においては、ノーマルモード/コモンモードの区別によらず、電流はインピーダンスが低いところ、すなわち流れやすい経路を流れているだけです。

このことを単純化すると以下のようにまとめることができます。

ノーマルモード電流 : 人間が考えた経路(=回路図に書かれた経路)を流れる電流

コモンモード電流 : 意図していない経路(=回路図に書かれていない経路)を流れる電流

このように単純化するとコモンモードノイズ(≒電流)とはどのようなものかが理解しやすくなると思います。

ここで、「なぜ意図しない経路に電流が流れるか?」が重要になります。コモンモードノイズが発生する要因を大別すると、以下の2つにまとめることができます。

(1)寄生・浮遊容量によるコモンモードノイズ

(2)伝送路の不完全性によるコモンモードノイズ

伝送路が不完全(平衡回路の不平衡成分、リターンGNDの不完全性など)な場合、コモンモード電圧が生じ、その電圧により意図しない経路に電流が流れることでコモンモードノイズが発生

この2つの要因を、もう少し掘り下げて考えてみましょう。

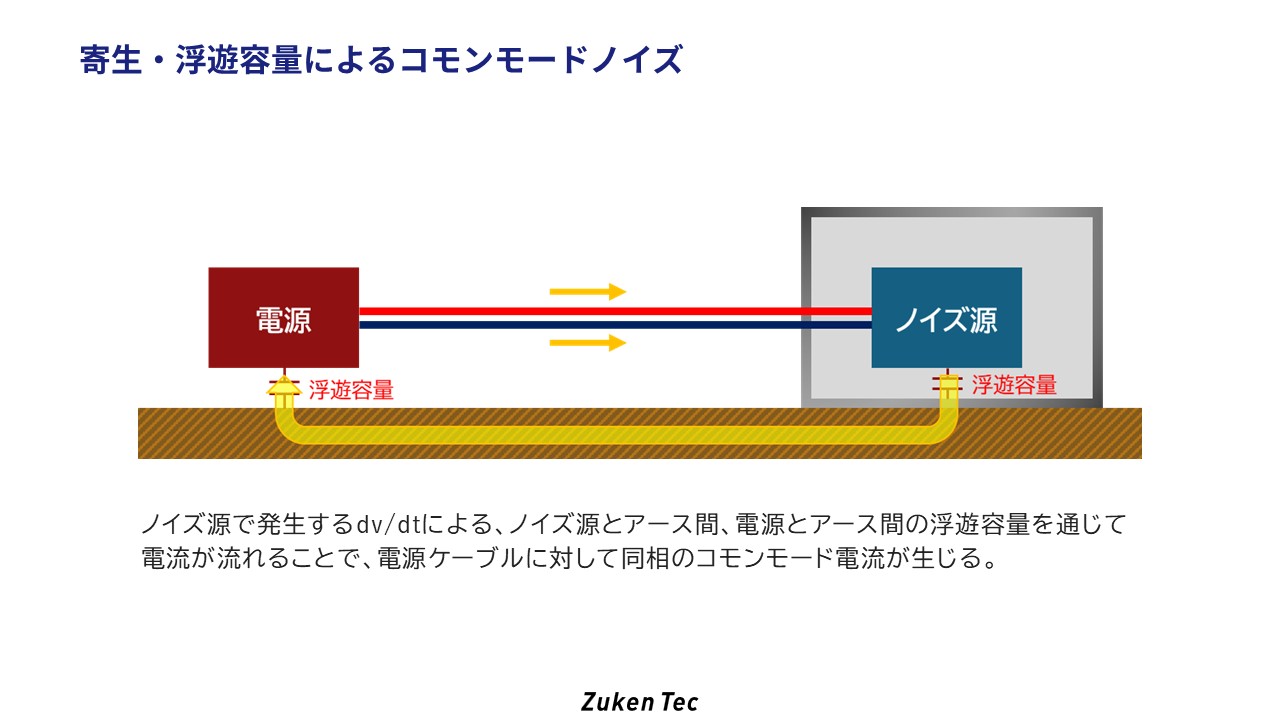

(1)寄生・浮遊容量によるコモンモードノイズについて、図のように信号源や負荷と筐体間の容量成分が存在すると、その容量からアースを通じて電流が流れます。

この電流がコモンモードノイズの要因となるコモンモード電流ですが、その量は容量成分とdv/dtの大きさに準じます。

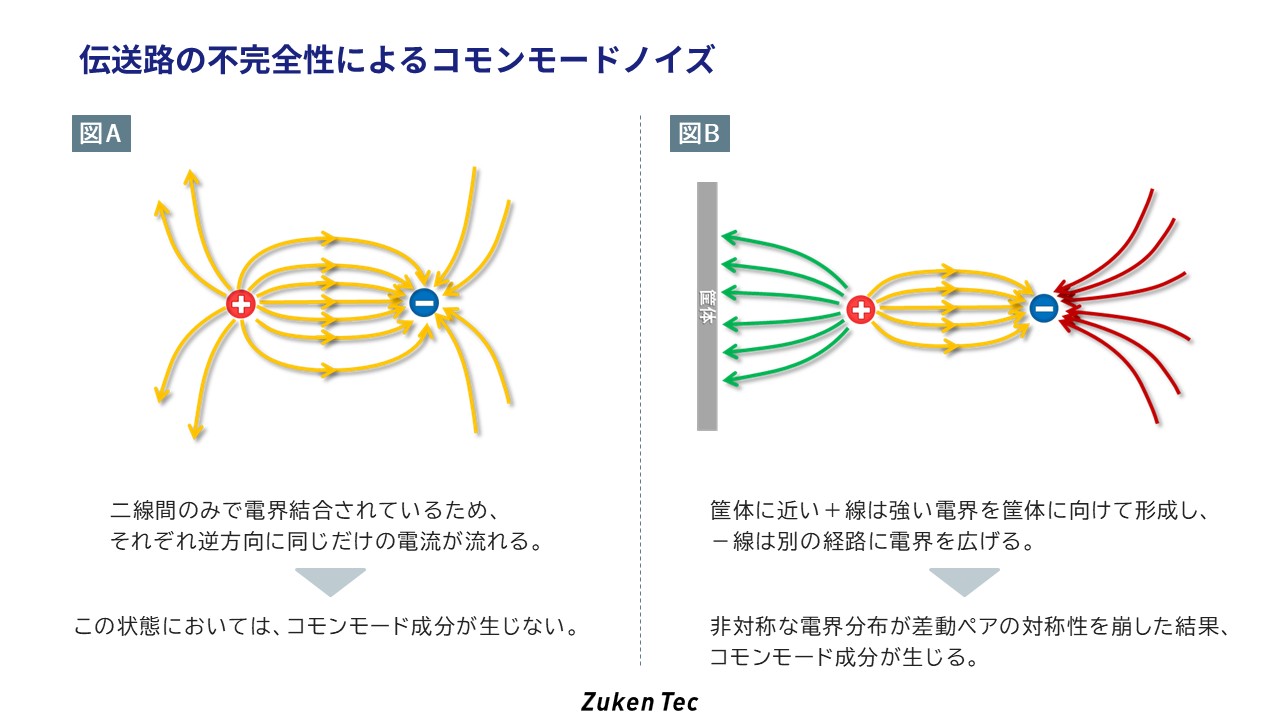

また、(2)伝送路の不完全性によるコモンモードノイズについて、平衡回路(差動信号)では、図Aのように二線間で電界結合している場合はノーマルモード電流が流れますが、二線間で結合しきれない電界結合がコモンモード電流の要因となります。

この図Aのような場合は、コモンモード電流が差動信号の二線間のすぐ近くを通るため、発生したコモンモード電流による磁界が相殺されるため、大きなノイズになりにくいですが、図Bのように二線間のバランスが崩れる様な場合に、電界分布が非対象となりコモンモード成分が増加します。

このようにコモンモードノイズは発生しますが、要因を理解することで有効な対策を施すことができます。

次にこの発生原理をパワエレに当てはめて、パワエレにおけるコモンモードノイズの発生要因とその対策について解説します。

パワエレにおけるコモンモードノイズ

パワエレの特徴は、高電圧・大電流をIGBTやMOSFETなどのスイッチングデバイスでスイッチングして回路を動作させていることです。この動作によるdv/dtとdi/dtがコモンモードノイズの要因となります。

このdv/dtとdi/dtがパワエレ回路でどのようにコモンモードノイズになるのか、またどのような対策を行うかについて解説します。

(1)パワエレにおけるdv/dt(電圧変動)とコモンモードノイズ

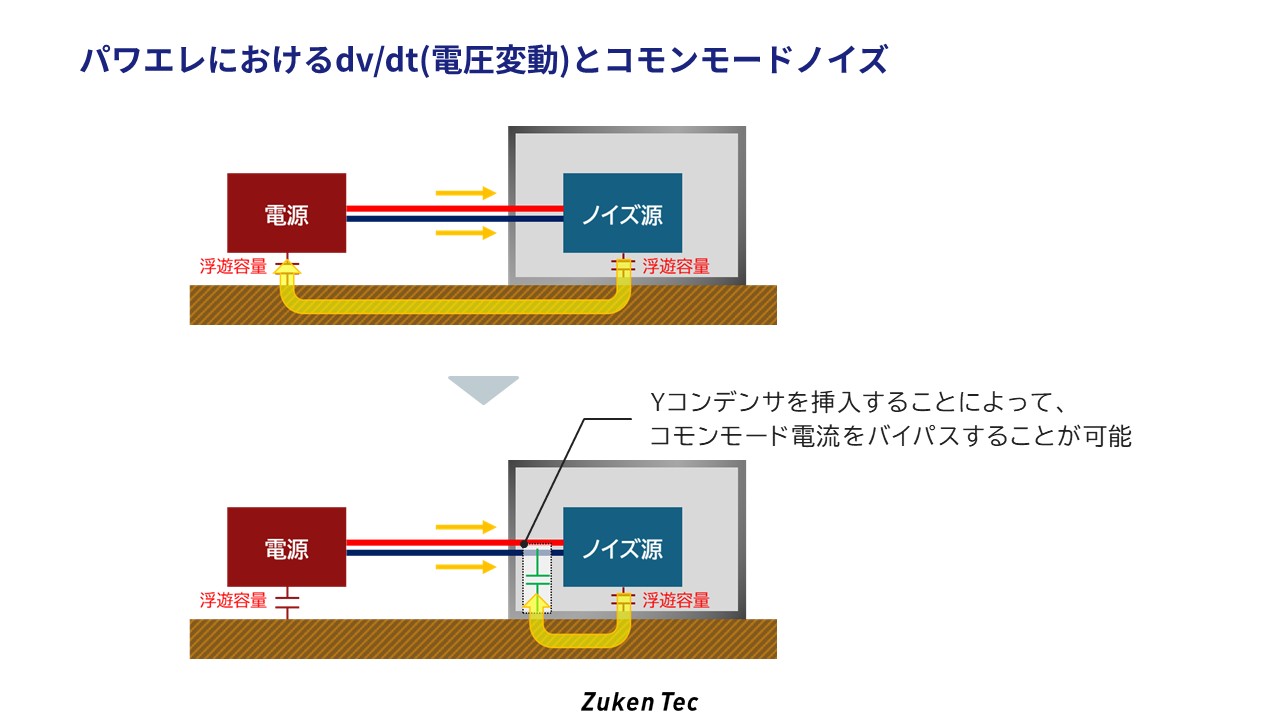

dv/dtがコモンモードノイズの要因となるのは、「コモンモードノイズとは」で解説した通り、スイッチングによる電圧変動(dv/dt)により、回路・負荷と筐体・アース間に存在する容量成分を経路として電流が流れるためです。

パワエレにおいて最も大きなdv/dtが発生する箇所は、当然ですがスイッチングを行っている主回路です。

そのため、パワエレのdv/dtによるコモンモードノイズを抑えるためには、このdv/dtそのものを小さくするか、コモンモード電流の経路となる容量成分を減らすことが対策の要です。

dv/dtを小さくする対策としては、ゲート抵抗を大きくするなど、ゲート駆動回路へ対策することでスイッチング速度を遅くする方法が考えられます。

ただし、スイッチング速度を遅くしすぎると損失が増えるなどデメリットも大きくなるため、むやみに遅くすることもできません。

また、寄生容量、浮遊容量の削減も有効な対策手段ですが、放熱や機械的な制約や部品・ユニットそのものに存在する寄生成分のために十分に削減することが困難な場合が多いです。

そのため、コモンモードノイズを削減するのにdv/dtや容量成分を十分に減少させることが難しい場合が多く、その場合の対策が重要です。「コモンモードノイズとは?」で触れた通り、コモンモードノイズ対策の難しさは、コモンモード電流の経路がわかりにくいことが要因です。

反対に、コモンモード電流の経路を把握することができれば、その経路を遮断することで有効な対策を施すことができます。

具体的には、図のように主回路で発生したdv/dtが主回路-筐体間の容量を経路にして、電源にコモンモード電流が流れる場合、この経路の途中にコモンモード電流をバイパスするコンデンサ(Yコンデンサ)を配置することで、電流ループを小さくしてコモンモードノイズを減らすことが可能です。

(2)パワエレでのdi/dt(電流変動)とコモンモードノイズ

パワエレでの電流変動によるコモンモードノイズは、dv/dtの場合と異なり、ノイズ発生のメカニズムが多少複雑になります。

その理由は、di/dtが直接コモンモードノイズになるケースと、di/dtによりノーマルモードノイズが発生し、それがモード変換によってコモンモードノイズになるケースがあるためです。

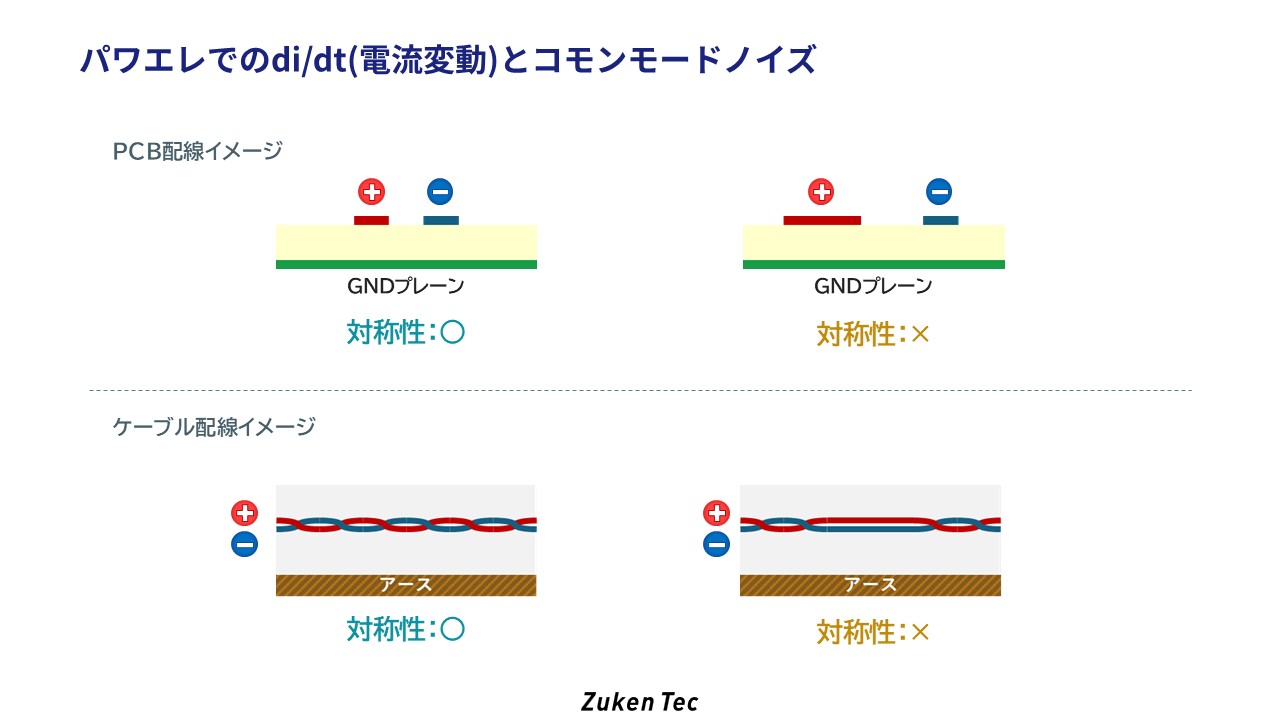

ただし、このどちらであっても、下図のようにPCB配線やケーブルの結合状態が完全でない場合にコモンモードノイズが増加するという共通点があります。

従って、di/dtに対する有効な対策は、電源ラインや出力ラインの結合を強くするとともに、対称性を高くすることでコモンモードノイズを削減することが可能です。

また、di/dtがノーマルモードノイズになるケースでは、ノーマルモードノイズ対策そのものが、コモンモードノイズ対策としても有効です。(ノーマルモードノイズへの対策は前回の記事を参照ください。)

コモンモードノイズのまとめ

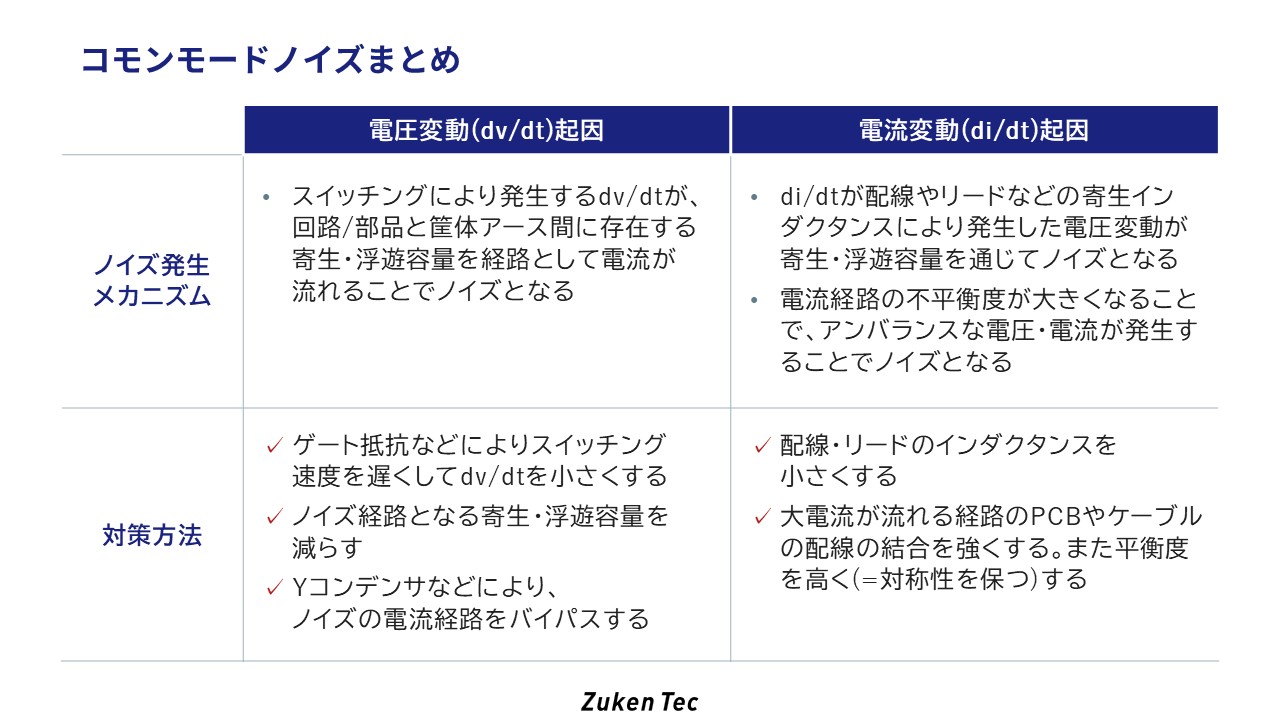

パワエレにおけるコモンモードノイズについてまとめると、以下のように表現することができます。

前回のノーマルモードノイズのまとめの際には、伝導/放射ノイズに分けて考えましたが、コモンモードノイズについては、このような切り分けをせずに解説しました。

その理由としては、コモンモードノイズは、電流がそのままLISNに伝わり伝導ノイズとなるか、電流経路がアンテナとなり電磁波となって放射ノイズとなるかの違いでしかなく、コモンモード電流を減らす、もしくは電流経路をコントロールすることが対策となるため、切り分けて考えずに伝導/放射ノイズをまとめて考えることが重要になります。

最後に

前回はノーマルモードノイズ、今回はコモンモードノイズについて解説を行いました。次回の記事では、このノーマルモード/コモンモードノイズがどのように伝わってEMIノイズとなるかについて解説する予定です。

連載記事一覧

<EMC設計関連>

-

- パワーエレクトロニクスにおけるEMC問題

- EMCにおける実装設計

- パワエレにおけるEMCノイズ(前編)

- パワエレにおけるEMCノイズ(後編) <本記事>

- パワエレにおけるノイズの伝わり方

- DC-DCコンバータにおけるノイズと基板レイアウト

<熱設計関連>

この記事の執筆者

図研テック株式会社 技術監督 古瀬 利之

iNARTE EMC Master Design Engineer (Certificate No.EMCD-00243-ME)

1999年株式会社図研プロセスデザイン研究所(現、図研テック株式会社)に入社。

EMC設計・対策、高速半導体用インターポーザ、携帯電話用PCBを中心に電気設計業務を担当。

2014年よりEMC設計支援サービスやEMC設計教育サービスを立ち上げ、2021年より現職。

-

- KEC関西電子工業振興センター

iNARTE EMC設計技術者資格試験問題作成部会委員(2016-2018) - KEC関西電子工業振興センター主催 設計者向けEMC技術講座

「EMC設計におけるフロントローディングとデザインレビュー」

講師(2016-2019) - 環境電磁工学研究会(EMCJ)主催

第14回 EMC基礎ワークショップ 講師(2018) - ポリテクセンター中部主催

ディジタル回路のEMC実践技術講座 講師(2021-) - 第31回エレクトロニクス実装学会春季講演大会

講演大会優秀賞受賞

受賞講演「部品内蔵基板設計におけるCAE活用と、テスト容易化設計技術の展望」

- KEC関西電子工業振興センター

提供サービスのご紹介

「EMC設計支援サービス」の詳しい説明は、こちらの資料をご覧ください。

EMC設計をはじめエンジニアの育成・スキルアップにご興味をお持ちの方は、

「eZラーニング(イージーラーニング)」のサービス紹介ページをご覧ください。

メールマガジン『ZUKEN TEC NEWS』では、

設計や解析技術、CAD運用に関する情報や、図研テックのエンジニアが登壇するセミナーのご案内などをお届けしています。